FIFO 下溢解析

FIFO下溢:读空fifo后继续读则导致下溢

大家可能遇到过这种情况,在调试过程中有些模块运行不正常,但不调试就没有问题

有点类似经典的双缝干涉实验:观察行为破坏了量子叠加态,或者说观测行为本身改变了系统的演化

不过我们接下来要谈论的问题没有上面的这么高深,一般情况下出现这个问题都是因为用户在调试界面打开了模块寄存器窗口,当断点触发时候,调试器会自动更新模块寄存器窗口数据,这个时候像SPI/UART的接收数据,ADC的转换数据等就会被调试器读走,这种数据寄存器一般都是FIFO实现的,读一个少一个,所以CPU读的时候就会少数据。调试器的这个操作一般也会被忽略,所以看起来就像是调试就有问题,不调试就没有问题。

下面是两个具体的事例:

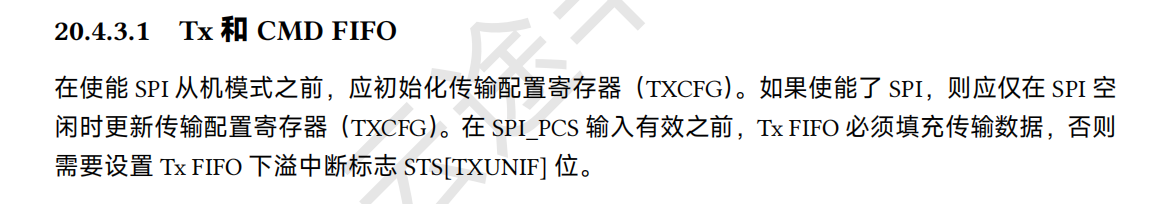

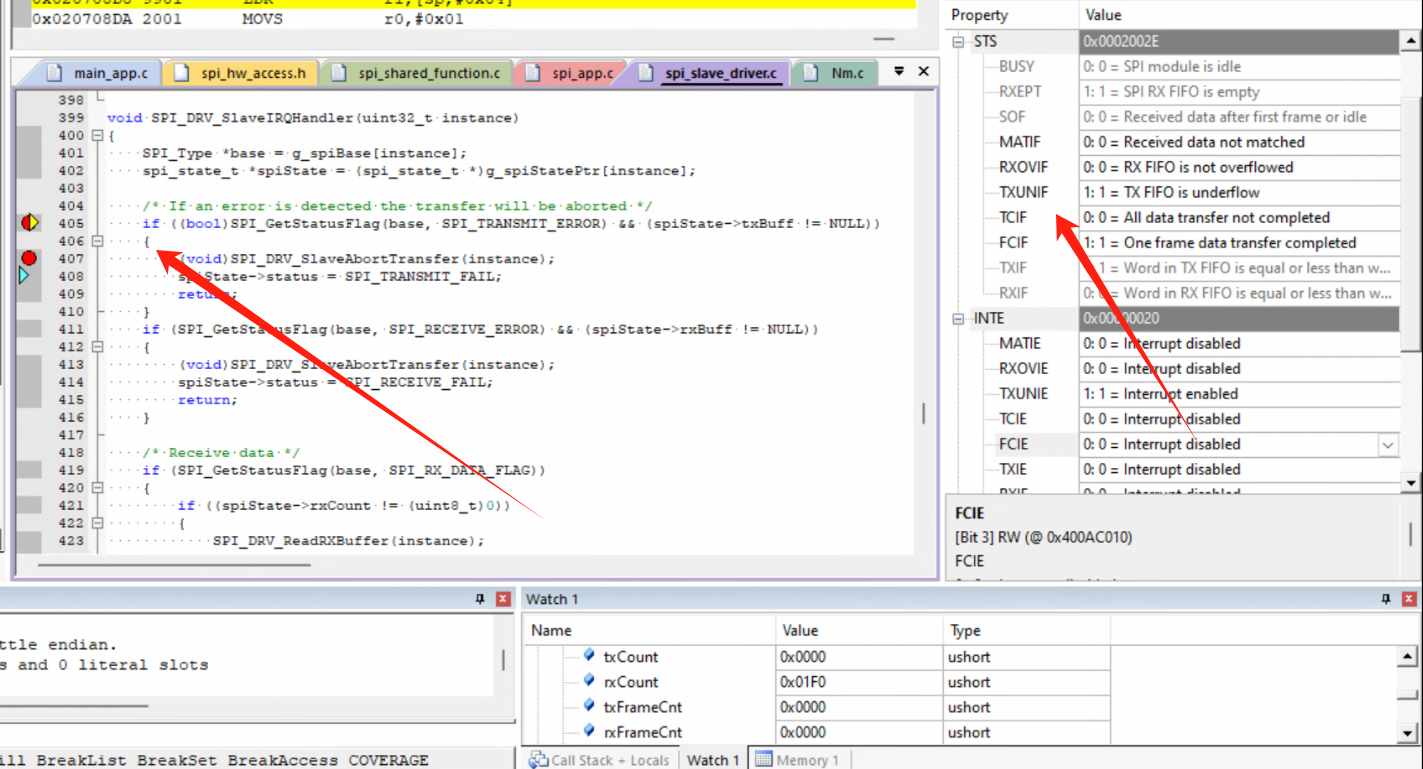

通过SPI->STS寄存器可以看到TX FIFO下溢标志位被置,但无法进SPI TRANSMIT ERROR的处理的 if 。spiState->txBuff == 0x00.且会一直进中断.

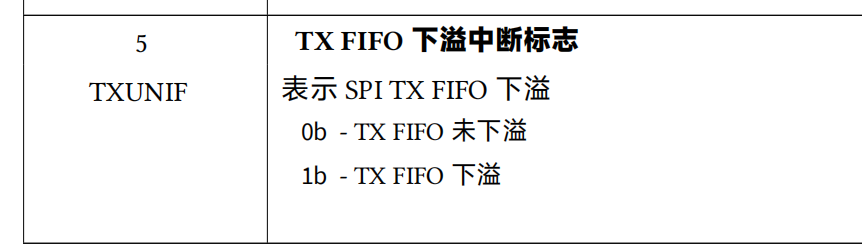

TXUNIF为 TX FIFO 下溢中断标志

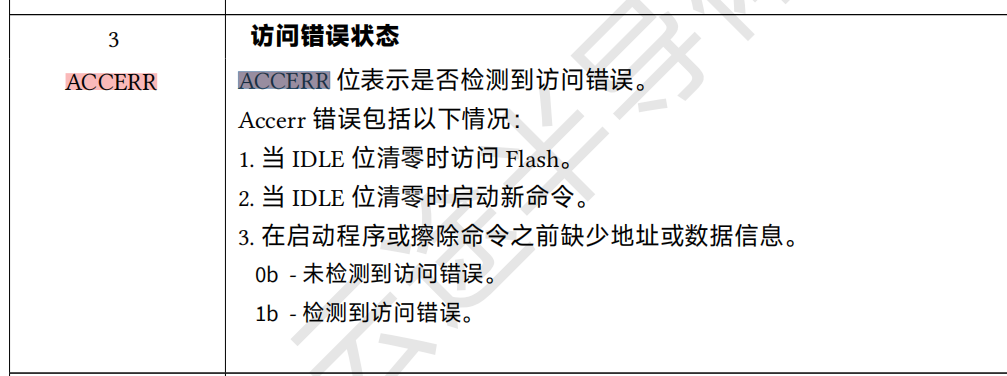

在擦写flash的过程中,打开了debug工具的memory窗口,可能会导致ACCERR。因为这个动作也相当于是读flash(虽然不是FIFO,不过感觉与本文思想非常相关)

还有一种情况会同样会触发下溢中断标志位,SPI在做从机时,在被片选前,就需要把TX FIFO里面的数据准备好,否则也可能会触发该中断