之前就听说CAN是一个趋近于完美的协议,但在学习这个协议的过程我很困惑,为什么计算波特率要分成这么多段,这些段都是做什么的呢?

其中有几个关键点:

同步段(SS,Sync_Seg)必须为1 Tq,用于信号边沿同步

同步跳转宽度(RJW, Resync jump width)尽可能大,但是不大于相位缓冲段2

ISO 11898-1:2015 规范中规定Phase_Seg2 的长度至少应等于信息处理时间(最小值为2Tq)

即PS2>2Tq

Prop_Seg:根据物理延迟计算,宁大勿小(过小会导致采样不稳定)。

Phase_Seg1:占总Tq的50% - 70%,确保足够的延长空间。

Phase_Seg2: ≥2 Tq,通常设为总Tq的20% - 30%。

采样点:控制在75%~90%位时间

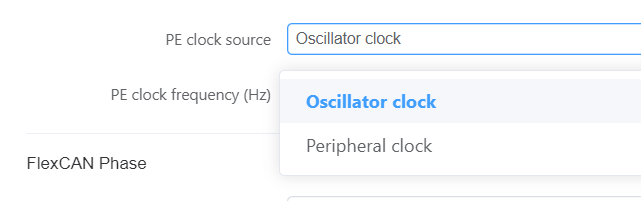

云途MCU的CAN时钟可以晶振或者外设时钟(fastbus clock 作为 CAN 模块时钟)

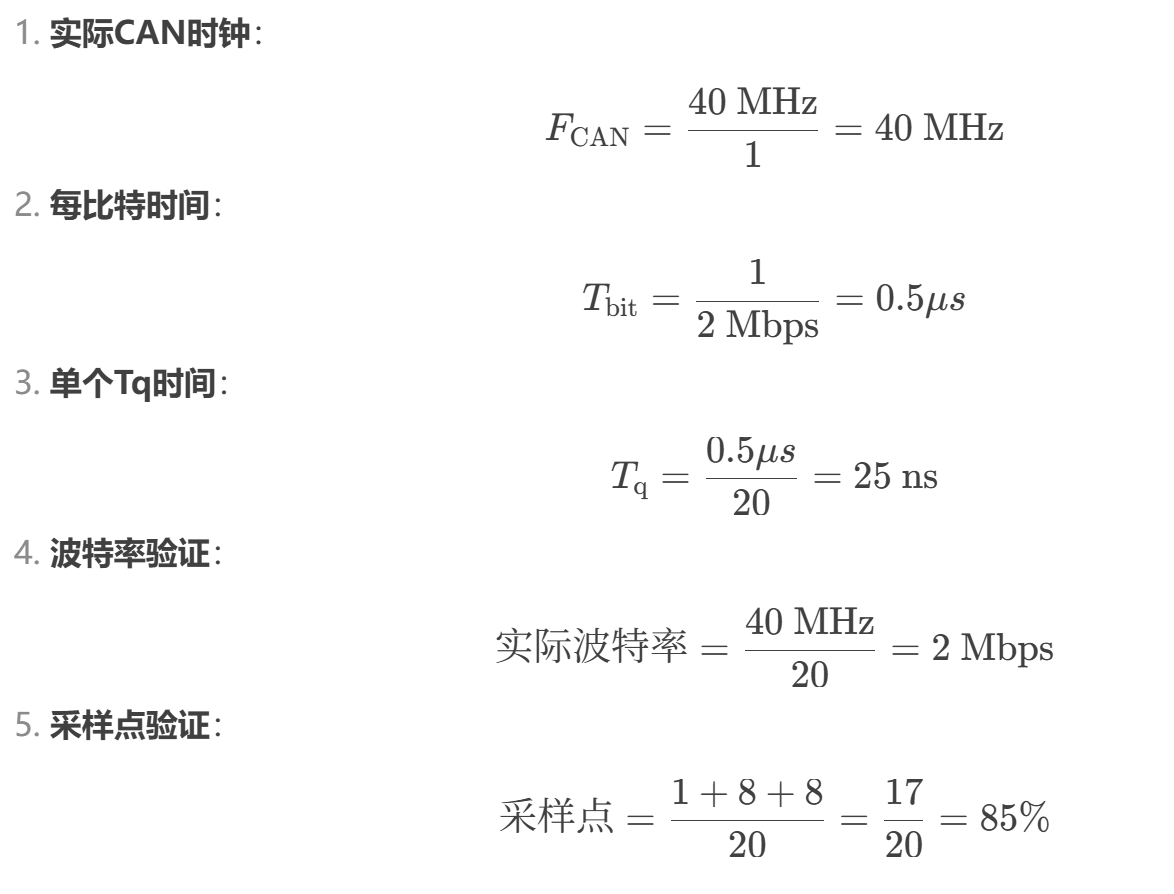

为便于理解,看一下下面的典型问题:波特率是500K,FXOSC时钟20M,CAN采样点无法设置到81.25%?

晶振频率:20 MHz 预分频 (BRP):2

我们可以计算出 Tq (时间量子) 长度

Tq = (BRP) / fCLK = 2 / 20,000,000 Hz = 0.0000001 秒 = 100 ns

位时间可以根据波特率(500K)来计算:

位时间 = 1 / 波特率 = 1 / 500,000 = 0.000002 秒 = 2000 ns

可以得到总Tq数

Total_Tq = 位时间 / Tq = 2000 ns / 100 ns = 20

这些固定约束决定了采样点位置只能以 5% (即 1/20 * 100%) 为步进单位进行调整。可实现的采样点位置只能是 75.0%, 80.0%, 85.0%, 90.0% 等,即上面所表述的CAN采样点无法设置到81.25%

说了这么多,到底什么是采样点呢?

想象一个CAN位时间(例如500kbps时为2μs):

1.起始时刻:总线电平开始变化(如从1→0)。

2.跳变区域:信号存在振荡(振铃)、上升/下降延迟(物理特性)。

3.稳定区域:信号趋于平稳(理想采样窗口)。

采样点需设置在稳定区域内,避开跳变区域:

采样点为何影响通信稳定性?

1.设置过早(如<70%)

- 采样时信号仍在跳变,易读错电平 → 误码率上升。

- 示例:若在50%采样,可能遇到振铃(Ringring)导致误判。

2.设置过晚(如>95%) - 接近下一位起始边沿,可能受时钟偏差累积影响 → 采样偏移到下一个位时间。

- 风险:错过当前位采样窗口。

3.理想范围 - Classic CAN:75%-90%(中低速,容忍长延迟)

- CAN FD:65%-85%(高速,需提前避开后续边沿)

通常来说主机厂都会规定采样点